# ATmega32 Reference Guide

Ver. 1.0 9-20-2005

### **1** Features

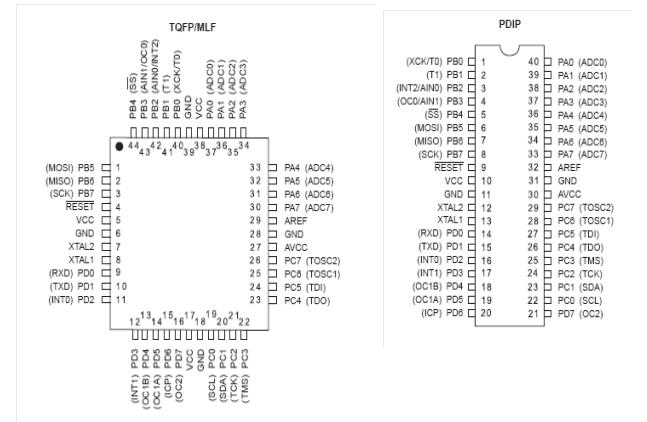

High-performance, Low-power RISC Architecture 8-bit Microcontroller 32 x 8 General Purpose Working Registers Fully Static Operation, up to 16 MIPS Throughput at 16 MHz On-chip 2-cycle Multiplier Nonvolatile Program and Data Memories 32K Bytes of In-System Self-Programmable Flash, Endurance: 10,000 Write/Erase Cycles Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program, true Read-While-Write Operation 1024 Bytes EEPROM, Endurance: 100,000 Write/Erase Cycles 2K Byte Internal SRAM Programming Lock for Software Security JTAG (IEEE std. 1149.1 Compliant) Interface, Boundary-scan Capabilities Extensive On-chip Debug Support, Programming of Flash, EEPROM, Fuses, and Lock Bits **Peripheral Features** Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode Real Time Counter with Separate Oscillator Four PWM Channels 8-channel, 10-bit ADC 8 Single-ended Channels, 7 Differential Channels in TQFP Package Only 2 Differential Channels with Programmable Gain at 1x, 10x, or 200x Byte-oriented Two-wire Serial Interface Programmable Serial USART Master/Slave SPI Serial Interface Programmable Watchdog Timer with Separate On-chip Oscillator **On-chip Analog Comparator** Special Microcontroller Features Power-on Reset and Programmable Brown-out Detection Internal Calibrated RC Oscillator External and Internal Interrupt Sources Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby I/O and Packages 32 Programmable I/O Lines 40-pin PDIP, 44-lead TQFP, and 44-pad MLF **Operating Voltages** 2.7 - 5.5V for ATmega32L 4.5 - 5.5V for ATmega32 Speed Grades 0 - 8 MHz for ATmega32L, 0 - 16 MHz for ATmega32 Power Consumption at 1 MHz, 3V, 25×C for ATmega32L Active: 1.1 mA Idle Mode: 0.35 mA Power-down Mode:< 1 ìA

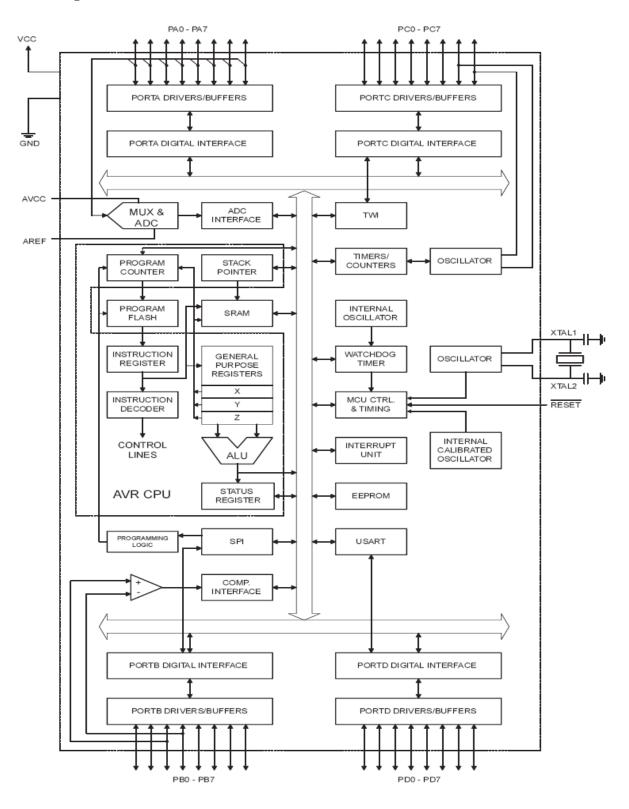

## 2 Block Diagram

# ATmega32 Reference Guide

# 3 Programming Model

| 1111115 | g wiodei | 7   |    |    | 0   | A 11  |   |                      |

|---------|----------|-----|----|----|-----|-------|---|----------------------|

|         |          | 7   |    |    | 0   | Addr. |   |                      |

|         |          |     | R  | .0 |     | \$00  |   |                      |

|         |          |     | R  | .1 |     | \$01  |   |                      |

|         |          |     | R  | .2 |     | \$02  |   |                      |

|         |          |     | R  | .3 |     | \$03  |   |                      |

|         |          |     |    |    |     |       |   |                      |

|         |          |     | R  | 12 |     | \$0C  |   |                      |

|         |          |     | R  | 13 |     | \$0D  |   |                      |

|         |          |     | R  | 14 |     | \$0E  |   |                      |

|         |          |     | R  | 15 |     | \$0F  |   |                      |

|         |          |     | R  | 16 |     | \$10  |   |                      |

|         |          |     | R  | 17 |     | \$11  |   |                      |

|         |          |     |    |    |     |       |   |                      |

|         |          |     | R2 | 26 |     | \$1A  |   | X-register Low Byte  |

|         |          |     | R2 | 27 |     | \$1B  |   | X-register High Byte |

|         |          |     | R2 | 28 |     | \$1C  |   | Y-register Low Byte  |

|         |          |     | R2 | 29 |     | \$1D  |   | Y-register High Byte |

|         |          |     | Râ | 30 |     | \$1E  |   | Z-register Low Byte  |

|         |          |     | Râ | 31 |     | \$1F  |   | Z-register High Byte |

| -       | 15       | XH  |    |    | XL  |       | 0 | _                    |

|         | 7        | R27 | 0  | 7  | R26 |       | 0 |                      |

| _       | 15       | YH  |    |    | YL  |       | 0 | -                    |

|         | 7        | R29 | 0  | 7  | R28 |       | 0 |                      |

| F       | 15       | ZH  |    | ſ  | ZL  |       | 0 | 7                    |

# Z-register

X-register

Y-register

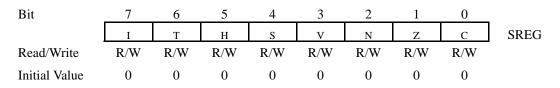

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | Ι   | Т   | Н   | S   | V   | Ν   | Z   | С   |

| Read/Write    | R/W |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

0

7

I - Global Interrupt Enable

R31

C - carry flag

7

N - Negative Flag

S - Sign Bit, S = N EXOR V

T - Bit Copy Storage

R30

Z - Zero Flag

V - Two's Complement Overflow Flag

0

H - Half Carry Flag

### 4 Interrupt Vector Assignments

| Vector No. | Program<br>Address | Source       | Interrupt                                                                            |

|------------|--------------------|--------------|--------------------------------------------------------------------------------------|

| 1          | \$0000             | RESET        | External Pin, Power-on Reset, Brown-out Reset, Watchdog Reset, and JTAG<br>AVR Reset |

| 2          | \$0002             | INT0         | External Interrupt Request 0                                                         |

| 3          | \$0004             | INT1         | External Interrupt Request 1                                                         |

| 4          | \$0006             | INT2         | External Interrupt Request 2                                                         |

| 5          | \$0008             | TIMER2 COMP  | Timer/Counter2 Compare Match                                                         |

| 6          | \$000A             | TIMER2 OVF   | Timer/Counter2 Overflow                                                              |

| 7          | \$000C             | TIMER1 CAPT  | Timer/Counter1 Capture Event                                                         |

| 8          | \$000E             | TIMER1 COMPA | Timer/Counter1 Compare Match A                                                       |

| 9          | \$0010             | TIMER1 COMPB | Timer/Counter1 Compare Match B                                                       |

| 10         | \$0012             | TIMER1 OVF   | Timer/Counter1 Overflow                                                              |

| 11         | \$0014             | TIMER0 COMP  | Timer/Counter0 Compare Match                                                         |

| 12         | \$0016             | TIMER0 OVF   | Timer/Counter0 Overflow                                                              |

| 13         | \$0018             | SPI STC      | Serial Transfer Complete                                                             |

| 14         | \$001A             | USART RXC    | USART, Rx Complete                                                                   |

| 15         | \$001C             | USART UDRE   | USART Data Register Empty                                                            |

| 16         | \$001E             | USART TXC    | USART, Tx Complete                                                                   |

| 17         | \$0020             | ADC          | ADC Conversion Complete                                                              |

| 18         | \$0022             | EE_RDY       | EEPROM Ready                                                                         |

| 19         | \$0024             | ANA_COMP     | Analog Comparator                                                                    |

| 20         | \$0026             | TWI          | Two-wire Serial Interface                                                            |

| 21         | \$0028             | SPM_RDY      | Store Program Memory Ready                                                           |

- When the BOOTRST fuse is programmed, the device will jump to the Boot Loader address at reset.

- When the IVSEL bit in GICR is set, interrupt vectors will be moved to the start of the Boot Flash section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash section.

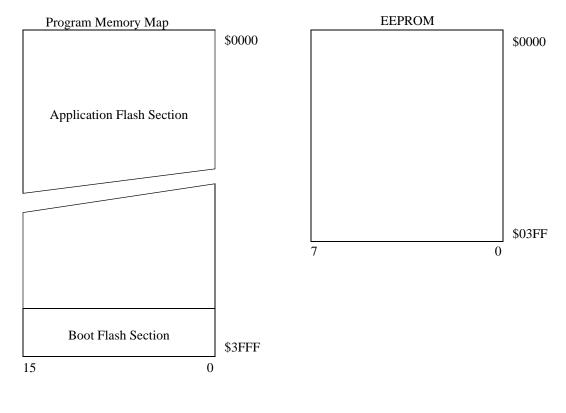

# 5 Memory Maps

| Data Address Space |

|--------------------|

| \$0000             |

| \$0001             |

|                    |

| \$001E             |

| \$001F             |

|                    |

| \$0020             |

| \$0021             |

|                    |

| \$005E             |

| \$005F             |

|                    |

| Internal SRAM |   |

|---------------|---|

| \$0060        |   |

| \$0061        |   |

|               |   |

| \$085E        |   |

| \$085F        |   |

| 7             | 0 |

# 5.1 Instruction Set

| Mnemonic       | Ops.         | Description                              | Operation                           | Flags       | Cyc. |

|----------------|--------------|------------------------------------------|-------------------------------------|-------------|------|

| Arithmetic and | l Logic Inst | ructions                                 |                                     |             |      |

| ADD            | Rd,Rr        | Add without carry                        | Rd=Rd+Rr                            | Z,C,N,V,H,S | 1    |

| ADC            | Rd,Rr        | Add with carry                           | Rd=Rd+Rr+C                          | Z,C,N,V,H,S | 1    |

| ADIW           | Rd,K         | Add immediate to word                    | Rd+1:Rd=Rd+1:Rd+K6<br>d=24,26,28,30 | Z,C,N,V,S   | 2    |

| SUB            | Rd,Rr        | Subtract without carry                   | Rd=Rd-Rr                            | Z,C,N,V,H,S | 1    |

| SUBI           | Rd,Rr        | Subtract immediate                       | Rd=Rd-K8 d=1631                     | Z,C,N,V,H,S | 1    |

| SBC            | Rd,Rr        | Subtract with carry                      | Rd=Rd-Rr-C                          | Z,C,N,V,H,S | 1    |

| SBCI           | Rd,K8        | Subtract with carry immediate            | Rd-Rd-K8-C d=1631                   | Z,C,N,V,H,S | 1    |

| SBIW           | Rd,K         | Subtract Immediate from Word             | Rd+1:Rd=Rd+1:Rd-K6<br>d=24,26,28,30 |             |      |

| AND            | Rd,Rr        | Logical AND                              | Rd=Rd AND Rr                        | Z,N,V,S     | 1    |

| ANDI           | Rd,K8        | Logical AND with immediate               | Rd=Rd AND k8 d=1631                 | Z,N,V,S     | 1    |

| OR             | Rd,Rr        | Logical OR                               | Rd=Rd OR Rr                         | Z,N,V,S     | 1    |

| ORI            | Rd,K8        | Logical OR with immediate                | Rd=Rd OR K8 d=1631                  | Z,N,V,S     | 1    |

| EOR            | Rd,Rr        | Logical EXOR                             | Rd=Rd EXOR Rr                       | Z,N,V,S     | 1    |

| COM            | Rd           | One's complement                         | Rd=\$FF-Rd                          | Z,C,N,V,S   | 1    |

| NEG            | Rd           | Two's complement                         | Rd=\$00-Rd                          | Z,C,N,V,H,S | 1    |

| SBR            | Rd,K8        | Set bit(s) in register                   | Rd=Rd OR K8                         | Z,C,N,V,S   | 1    |

| CBR            | Rd,k8        | Clear bit(s) in register                 | Rd=Rd*(\$FF-k8) d=1631              | Z,C,N,V,S   | 1    |

| INC            | Rd           | Increment register                       | Rd=Rd+1                             | Z,N,V,S     | 1    |

| DEC            | Rd           | Decrement register                       | Rd=Rd-1                             | Z,N,V,S     | 1    |

| TST            | Rd           | Test for zero or negative                | Rd=Rd AND RD                        | Z,C,N,V,S   | 1    |

| CLR            | Rd           | Clear register                           | Rd=0                                | Z,C,N,V,S   | 1    |

| SER            | Rd           | Set register                             | Rd=\$FF d=1631                      | None        | 1    |

| SBIW           | Rd,K6        | Subtract immediate from word             | Rd+1:Rd=Rd+1:Rd-k6                  | Z,C,N,V,S   | 2    |

| MUL            | Rd,Rd        | Multiply unsigned                        | R1:R0=Rd*Rr                         | Z,C         | 2    |

| MULS           | Rd,Rr        | Multiply signed                          | R1:R0=Rd*Rr                         | Z,C         | 2    |

| MULSU          | Rd,Rr        | Multiply signed with unsigned            | R1:R0=Rd*Rr                         | Z,C         | 2    |

| FMUL           | Rd,Rr        | Fractional multiply unsigned             | R1:R0=(Rd*Rr)<<1                    | Z,C         | 2    |

| FMULS          | Rd,Rr        | Fractional multiply signed               | R1:R0=(Rd*Rr)<<1                    | Z,C         | 2    |

| FMULSU         | Rd,Rr        | Fractional multiply signed with unsigned | R1:R0=(Rd*Rr)<<1                    | Z,C         | 2    |

| Mnemonic       | Ops.  | Description                              | Operation                                 | Flags       | Cyc.  |

|----------------|-------|------------------------------------------|-------------------------------------------|-------------|-------|

| Branch Instruc | tions |                                          |                                           |             |       |

| RJMP           | K     | Relative Jump                            | PC=PC+K+1 k= -2k2k                        | None        | 2     |

| IJMP           | None  | Indirect Jump to (Z)                     | PC=Z                                      | None        | 2     |

| EIJMP          | None  | Extended Indirect Jump to (Z)            | Stack=PC+1, PC(15:0)=Z,<br>PC(21:16)=EIND | None        | 2     |

| JMP            | K     | Jump                                     | PC=K                                      | None        | 3     |

| RCALL          | К     | Relative Call Subroutine                 | Stack=PC+1, PC=PC+K+1<br>k= -2k2k         | None        | 3/4   |

| ICALL          | None  | Indirect Call to (Z)                     | Stack=PC+1, PC=(Z)                        | None        | 3/4   |

| CALL           | К     | Call Subroutine                          | Stack=PC+2, PC=K                          | None        | 4/5   |

| RET            | None  | Subroutine Return                        | PC=Stack                                  | None        | 4/5   |

| RETI           | None  | Interrupt Return                         | PC=Stack                                  | Ι           | 4/5   |

| CPSE           | Rd,Rr | Compare, Skip if Equal                   | if(Rd==Rr) PC=PC+2/3                      | None        | 1/2/3 |

| СР             | Rd,Rr | Compare                                  | Rd-Rr                                     | Z,C,N,V,H,S | 1     |

| CPC            | Rd,Rr | Compare with Carry                       | Rd-Rr-C                                   | Z,C,N,V,H,S | 1     |

| CPI            | Rd,K8 | Compare with Immediate                   | Rd-K8 d=1631                              | Z,C,N,V,H,S | 1     |

| SBRC           | Rr,b  | Skip if bit in register cleared          | if(Rr(b)==0) PC=PC+2/3 b=07               | None        | 1/2/3 |

| SBRS           | Rr,b  | Skip if bit in register set              | if(Rr(b)==1) PC=PC+2/3 b=07               | None        | 1/2/3 |

| SBIC           | P,b   | Skip if bit in I/O register cleared      | if(I/O(P,b)==0) PC=PC+2/3 b=07            | None        | 1/2/3 |

| SBIS           | P,b   | Skip if bit in I/O register set          | if(I/O(P,b)==1) PC=PC+2/3 b=07            | None        | 1/2/3 |

| BRBC           | s,k   | Branch if Status flag cleared            | if(SREG(s)==0) PC = PC + k + 1            | None        | 1/2   |

|                |       |                                          | k= -6463                                  |             |       |

| BRBS           | s,k   | Branch if Status flag set                | if(SREG(s)==1) PC = PC + k + 1            | None        | 1/2   |

|                |       |                                          | k= -6463                                  |             |       |

| BREQ           | k     | Branch if equal                          | if(Z==1) PC = PC + k + 1                  | None        | 1/2   |

|                |       |                                          | k=-6463                                   |             |       |

| BRNE           | k     | Branch if not equal                      | if(Z==0) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRCS           | k     | Branch if carry set                      | if(C==1) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRCC           | k     | Branch if carry cleared                  | if(C==0) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRSH           | k     | Branch if same or higher                 | if(C==0) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRLO           | k     | Branch if lower                          | if(C==1) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRMI           | k     | Branch if minus                          | if(N==1) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRPL           | k     | Branch if plus                           | if(N==0) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRGE           | k     | Branch if greater than or equal (signed) | if(S==0) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRLT           | k     | Branch if less than (signed)             | if(S==1) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRHS           | k     | Branch if half carry flag set            | if (H==1) PC = PC + $k$ + 1 $k$ = -6463   | None        | 1/2   |

| BRHC           | k     | Branch if half carry flag set            | if(H==1) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRTS           | k     | Branch if T flag set                     | if $(T==1)$ PC = PC + k + 1 k= -6463      | None        | 1/2   |

| BRTC           | k     | Branch if T flag cleared                 | if(T==0) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRVS           | k     | Branch if overflow flag set              | if(V==1) PC = PC + k + 1 k = -6463        | None        | 1/2   |

| BRVC           | k     | Branch if overflow flag cleared          | if (V==0) PC = PC + $k$ + 1 $k$ = -6463   | None        | 1/2   |

| BRIE           | k     | Branch if interrupt enabled              | if(I==1) PC = PC + $k$ + 1 $k$ = -6463    | None        | 1/2   |

| BRID           | k     | Branch if interrupt disabled             | if(I==0) $PC = PC + k + 1 k = -6463$      | None        | 1/2   |

| Mnemonic        | Operands    | Description                                 | Operation                             | Flags | Cyc. |

|-----------------|-------------|---------------------------------------------|---------------------------------------|-------|------|

| Data Transfer I | nstructions |                                             |                                       |       |      |

| MOV             | Rd,Rr       | Copy register                               | Rd=Rr                                 | None  | 1    |

| MOVW            | Rd,Rr       | Copy register pair                          | Rd+1:Rd=Rr+1:Rr, r,d even             | None  | 1    |

| LDI             | Rd,K8       | Load immediate                              | Rd=K d=1631                           | None  | 1    |

| LDS             | Rd,K        | Load Direct                                 | Rd=(K)                                | None  | 2    |

| LD              | Rd,X        | Load Indirect                               | Rd = (X)                              | None  | 2    |

| LD              | Rd,X+       | Load Indirect and Post-Increment            | Rd = (X), X=X+1                       | None  | 2    |

| LD              | Rd,-X       | Load Indirect and Pre-Decrement             | X=X-1, Rd = (X)                       | None  | 2    |

| LD              | Rd,Y        | Load Indirect                               | Rd = (Y)                              | None  | 2    |

| LD              | Rd,Y+       | Load Indirect and Post-Increment            | Rd = (Y), Y = Y + 1                   | None  | 2    |

| LD              | Rd,-Y       | Load Indirect and Pre-Decrement             | Y = Y - 1, Rd = (Y)                   | None  | 2    |

| LDD             | Rd,Y+q      | Load Indirect with displacement             | Rd = (Y+q)                            | None  | 2    |

| LD              | Rd,Z        | Load Indirect                               | Rd = (Z)                              | None  | 2    |

| LD              | Rd,Z+       | Load Indirect and Post-Increment            | Rd = (Z), Z=Z+1                       | None  | 2    |

| LD              | Rd,-Z       | Load Indirect and Pre-Decrement             | Z=Z-1, Rd = (Z)                       | None  | 2    |

| LDD             | Rd,Z+q      | Load Indirect with displacement             | Rd = (Z+q)                            | None  | 2    |

| STS             | k,Rr        | Store Direct                                | $(\mathbf{k}) = \mathbf{R}\mathbf{r}$ | None  | 2    |

| ST              | X,Rr        | Store Indirect                              | (X) = Rr                              | None  | 2    |

| ST              | X+,Rr       | Store Indirect and Post-Increment           | (X) = Rr, X = X + 1                   | None  | 2    |

| ST              | -X,Rr       | Store Indirect and Pre-Decrement            | X=X-1, (X)=Rr                         | None  | 2    |

| ST              | Y,Rr        | Store Indirect                              | $(\mathbf{Y}) = \mathbf{R}\mathbf{r}$ | None  | 2    |

| ST              | Y+,Rr       | Store Indirect and Post-Increment           | (Y) = Rr, Y = Y + 1                   | None  | 2    |

| ST              | -Y,Rr       | Store Indirect and Pre-Decrement            | Y=Y-1, (Y) = Rr                       | None  | 2    |

| ST              | Y+q,Rr      | Store Indirect with displacement            | (Y+q) = Rr                            | None  | 2    |

| ST              | Z,Rr        | Store Indirect                              | (Z) = Rr                              | None  | 2    |

| ST              | Z+,Rr       | Store Indirect and Post-Increment           | (Z) = Rr, Z = Z + 1                   | None  | 2    |

| ST              | -Z,Rr       | Store Indirect and Pre-Decrement            | Z=Z-1, (Z) = Rr                       | None  | 2    |

| ST              | Z+q,Rr      | Store Indirect with displacement            | (Z+q) = Rr                            | None  | 2    |

| LPM             | None        | Load Program Memory                         | $R0 = (\underline{Z})$                | None  | 3    |

| LPM             | Rd,Z        | Load Program Memory                         | $Rd = (\underline{Z})$                | None  | 3    |

| LPM             | Rd,Z+       | Load Program Memory and Post-Incre-<br>ment | $Rd = (\mathbb{Z}), Z = Z + 1$        | None  | 3    |

| SPM             | None        | Store Program Memory                        | $(\underline{Z}) = R1:R0$             | None  | -    |

| IN              | Rd,P        | In Port                                     | Rd = P                                | None  | 1    |

| OUT             | P,Rr        | Out Port                                    | P = Rr                                | None  | 1    |

| Mnemonic         | Operands    | Description                | Operation                       | Flags       | Cyc. |

|------------------|-------------|----------------------------|---------------------------------|-------------|------|

| Bit and Bit-Test | Instruction |                            |                                 |             |      |

| LSL              | Rd          | Logical shift left         | Rd(n+1)=Rd(n), Rd(0)=0, C=Rd(7) | Z,C,N,V,H,S | 1    |

| LSR              | Rd          | Logical shift right        | Rd(n)=Rd(n+1), Rd(7)=0, C=Rd(0) | Z,C,N,V,S   | 1    |

| ROL              | Rd          | Rotate left through carry  | Rd(0)=C, Rd(n+1)=Rd(n), C=Rd(7) | Z,C,N,V,H,S | 1    |

| ROR              | Rd          | Rotate right through carry | Rd(7)=C, Rd(n)=Rd(n+1), C=Rd(0) | Z,C,N,V,S   | 1    |

# ATmega32 Reference Guide

| Mnemonic | Operands | Description                  | Operation                        | Flags     | Cyc. |

|----------|----------|------------------------------|----------------------------------|-----------|------|

| ASR      | Rd       | Arithmetic shift right       | Rd(n)=Rd(n+1), n=0,,6            | Z,C,N,V,S | 1    |

| SWAP     | Rd       | Swap nibbles                 | Rd(30) = Rd(74), Rd(74) = Rd(30) | None      | 1    |

| BSET     | S        | Set flag                     | SREG(s) = 1                      | SREG(s)   | 1    |

| BCLR     | s        | Clear flag                   | SREG(s) = 0                      | SREG(s)   | 1    |

| SBI      | P,b      | Set bit in I/O register      | I/O(P,b) = 1 P=031 b =07         | None      | 2    |

| CBI      | P,b      | Clear bit in I/O register    | I/O(P,b) = 0 P=031 b=07          | None      | 2    |

| BST      | Rr,b     | Bit store from register to T | T = Rr(b)                        | Т         | 1    |

| BLD      | Rd,b     | Bit load from register to T  | Rd(b) = T                        | None      | 1    |

| SEC      | None     | Set carry flag               | C =1                             | С         | 1    |

| CLC      | None     | Clear carry flag             | $\mathbf{C} = 0$                 | С         | 1    |

| SEN      | None     | Set negative flag            | N = 1                            | N         | 1    |

| CLN      | None     | Clear negative flag          | $\mathbf{N} = 0$                 | N         | 1    |

| SEZ      | None     | Set zero flag                | Z = 1                            | Ζ         | 1    |

| CLZ      | None     | Clear zero flag              | Z = 0                            | Z         | 1    |

| SEI      | None     | Set interrupt flag           | I = 1                            | Ι         | 1    |

| CLI      | None     | Clear interrupt flag         | I = 0                            | Ι         | 1    |

| SES      | None     | Set signed flag              | S = 1                            | S         | 1    |

| CLN      | None     | Clear signed flag            | $\mathbf{S} = 0$                 | S         | 1    |

| SEV      | None     | Set overflow flag            | V = 1                            | V         | 1    |

| CLV      | None     | Clear overflow flag          | $\mathbf{V} = 0$                 | V         | 1    |

| SET      | None     | Set T-flag                   | T = 1                            | Т         | 1    |

| CLT      | None     | Clear T-flag                 | T = 0                            | Т         | 1    |

| SEH      | None     | Set half carry flag          | H = 1                            | Н         | 1    |

| CLH      | None     | Clear half carry flag        | H = 0                            | Н         | 1    |

| NOP      | None     | No operation                 | None                             | None      | 1    |

| SLEEP    | None     | Sleep                        | See instruction manual           | None      | 1    |

| WDR      | None     | Watchdog Reset               | See instruction manual           | None      | 1    |

| BREAK    | None     | Execution Break              | See instruction manual           | None      | 1    |

Rd: Destination (and source) register in the register file

Rr: Source register in the register file

b: Constant (0-7), can be a constant expression

s: Constant (0-7), can be a constant expression

P: Constant (0-31/63), can be a constant expression

K6; Constant (0-63), can be a constant expression

K8: Constant (0-255), can be a constant expression

k: Constant, value range depending on instruction. Can be a constant expression

q: Constant (0-63), can be a constant expression

Rdl: R24, R26, R28, R30. For ADIW and SBIW instructions

X,Y,Z: Indirect address registers (X=R27:R26, Y=R29:R28, Z=R31:R30)

# 6 Register Summary

| Address    | Name   | Bit7          | Bit6                                   | Bit5            | Bit4        | Bit3       | Bit2   | Bit1   | Bit0   |  |  |  |

|------------|--------|---------------|----------------------------------------|-----------------|-------------|------------|--------|--------|--------|--|--|--|

| \$3F(\$5F) | SREG   | Ι             | Т                                      | Н               | S           | V          | N      | Ζ      | С      |  |  |  |

| \$3E(\$5E) | SPH    | -             | -                                      | -               | -           | SP11       | SP10   | SP9    | SP8    |  |  |  |

| \$3D(\$5D) | SPL    | SP7           | SP6                                    | SP5             | SP4         | SP3        | SP2    | SP1    | SP0    |  |  |  |

| \$3C(\$5C) | OCR0   | Timer/Counter | Timer/Counter0 Output Compare Register |                 |             |            |        |        |        |  |  |  |

| \$3B(\$5B) | GICR   | INT1          | INT0                                   | INT2            | -           | -          | -      | IVSEL  | IVCE   |  |  |  |

| \$3A(\$5A) | GIFR   | INTF1         | INTF0                                  | INTF2           | -           | -          | -      | -      | -      |  |  |  |

| \$39(\$59) | TIMSK  | OCIE2         | TOIE2                                  | TICIE1          | OCIE1A      | OCIE1B     | TOIE1  | OCIE0  | TOIE0  |  |  |  |

| \$38(\$58) | TIFR   | OCF2          | TOV2                                   | ICF1            | OCF1A       | OCF1B      | TOV1   | OCF0   | TOV0   |  |  |  |

| \$37(\$57) | SPMCR  | SPMIE         | RWWSB                                  | -               | RWWSRE      | BLBSET     | PGWRT  | PGERS  | SPMEN  |  |  |  |

| \$36(\$56) | TWCR   | TWINT         | TWEA                                   | TWSTA           | TWSTO       | TWWC       | TWEN   | -      | TWIE   |  |  |  |

| \$35(\$55) | MCUCR  | SE            | SM2                                    | SM1             | SM0         | ISC11      | ISC10  | ISC01  | ISC00  |  |  |  |

| \$34(\$54) | MCUCSR | JTD           | ISC2                                   | -               | JTRF        | WDRF       | BORF   | EXTRF  | PORF   |  |  |  |

| \$33(\$53) | TCCR0  | FOC0          | WGM00                                  | COM01           | COM00       | WGM01      | CS02   | CS01   | CS00   |  |  |  |

| \$32(\$52) | TCNT0  | Timer/Counter | er0 (8 Bits)                           |                 |             | 1          |        |        |        |  |  |  |

| \$31(\$51) | OSCCAL | Oscillator Ca | libration Regist                       | er              |             |            |        |        |        |  |  |  |

|            | OCDR   | On-Chip Deb   | ug Register                            |                 |             |            |        |        |        |  |  |  |

| \$30(\$50) | SFIOR  | ADTS2         | ADTS1                                  | ADTS0           | _           | ACME       | PUD    | PSR2   | PSR10  |  |  |  |

| \$2F(\$4F) | TCCR1A | COM1A1        | COM1A0                                 | COM1B1          | COM1B0      | FOC1A      | FOC1B  | WGM11  | WGM10  |  |  |  |

| \$2E(\$4E) | TCCR1B | ICNC1         | ICES1                                  | -               | WGM13       | WGM12      | CS12   | CS11   | CS10   |  |  |  |

| \$2D(\$4D) | TCNT1H | Timer/Counter | er1 – Counter R                        | egister High By | rte         |            |        |        |        |  |  |  |

| \$2C(\$4C) | TCNT1L | Timer/Counter | er1 – Counter R                        | egister Low By  | te          |            |        |        |        |  |  |  |

| \$2B(\$4B) | OCR1AH | Timer/Counter | er1 – Output Co                        | mpare Register  | A High Byte |            |        |        |        |  |  |  |

| \$2A(\$4A) | OCR1AL | Timer/Counter | er1 – Output Co                        | mpare Register  | A Low Byte  |            |        |        |        |  |  |  |

| \$29(\$49) | OCR1BH | Timer/Counter | er1 – Output Co                        | mpare Register  | B High Byte |            |        |        |        |  |  |  |

| \$28(\$48) | OCR1BL | Timer/Counter | er1 – Output Co                        | mpare Register  | B Low Byte  |            |        |        |        |  |  |  |

| \$27(\$47) | ICR1H  | Timer/Counter | er1 – Input Capt                       | ure Register Hi | gh Byte     |            |        |        |        |  |  |  |

| \$26(\$46) | ICR1L  | Timer/Counter | er1 – Input Capt                       | ure Register Lo | ow Byte     |            |        |        |        |  |  |  |

| \$25(\$45) | TCCR2  | FOC2          | WGM20                                  | COM21           | COM20       | WGM21      | CS22   | CS21   | CS20   |  |  |  |

| \$24(\$44) | TCNT2  | Timer/Counter | er2 (8 Bits)                           |                 |             |            |        |        |        |  |  |  |

| \$23(\$43) | OCR2   | Timer/Counter | er2 Output Com                         | pare Register   |             |            |        |        |        |  |  |  |

| \$22(\$42) | ASSR   | -             | -                                      | -               | -           | AS2        | TCN2UB | OCR2UB | TCR2UB |  |  |  |

| \$21(\$41) | WDTCR  | _             | _                                      | _               | WDTOE       | WDE        | WDP2   | WDP1   | WDP0   |  |  |  |

| \$20(\$40) | UBRRH  | URSEL         | _                                      | _               | _           | UBRR[11:8] |        |        |        |  |  |  |

| UCSRC      | URSEL  | UMSEL         | UPM1                                   | UPM0            | USBS        | UCSZ1      | UCSZ0  | UCPOL  | 160    |  |  |  |

| \$1F(\$3F) | EEARH  | -             | -                                      | -               | -           | _          | _      | EEAR9  | EEAR8  |  |  |  |

| \$1E(\$3E) | EEARL  | EEPROM Ad     | dress Register                         | Low Byte        |             | 1          | 1      | 1      | 1      |  |  |  |

| \$1D(\$3D) | EEDR   | EEPROM Da     | ta Register                            |                 |             |            |        |        |        |  |  |  |

| \$1C(\$3C) | EECR   | -             | -                                      | _               | -           | EERIE      | EEMWE  | EEWE   | EERE   |  |  |  |

| \$1B(\$3B) | PORTA  | PORTA7        | PORTA6                                 | PORTA5          | PORTA4      | PORTA3     | PORTA2 | PORTA1 | PORTA0 |  |  |  |

| \$1A(\$3A) | DDRA   | DDA7          | DDA6                                   | DDA5            | DDA4        | DDA3       | DDA2   | DDA1   | DDA0   |  |  |  |

| \$19(\$39) | PINA   | PINA7         | PINA6                                  | PINA5           | PINA4       | PINA3      | PINA2  | PINA1  | PINA0  |  |  |  |

| \$18(\$38) | PORTB  | PORTB7        | PORTB6                                 | PORTB5          | PORTB4      | PORTB3     | PORTB2 | PORTB1 | PORTB0 |  |  |  |

| \$17(\$37) | DDRB   | DDB7          | DDB6                                   | DDB5            | DDB4        | DDB3       | DDB2   | DDB1   | DDB0   |  |  |  |

# ATmega32 Reference Guide

| Address    | Name   | Bit7         | Bit6                                    | Bit5     | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |  |  |

|------------|--------|--------------|-----------------------------------------|----------|--------|--------|--------|--------|--------|--|--|

| \$16(\$36) | PINB   | PINB7        | PINB6                                   | PINB5    | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  |  |  |

| \$15(\$35) | PORTC  | PORTC7       | PORTC6                                  | PORTC5   | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 |  |  |

| \$14(\$34) | DDRC   | DDC7         | DDC6                                    | DDC5     | DDC4   | DDC3   | DDC2   | DDC1   | DDC0   |  |  |

| \$13(\$33) | PINC   | PINC7        | PINC6                                   | PINC5    | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  |  |  |

| \$12(\$32) | PORTD  | PORTD7       | PORTD6                                  | PORTD5   | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 |  |  |

| \$11(\$31) | DDRD   | DDD7         | DDD6                                    | DDD5     | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   |  |  |

| \$10(\$30) | PIND   | PIND7        | PIND6                                   | PIND5    | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  |  |  |

| \$0F(\$2F) | SPDR   | SPI Data Reg | ister                                   |          |        |        |        |        |        |  |  |

| \$0E(\$2E) | SPSR   | SPIF         | WCOL                                    | -        | -      | -      | -      | -      | SPI2X  |  |  |

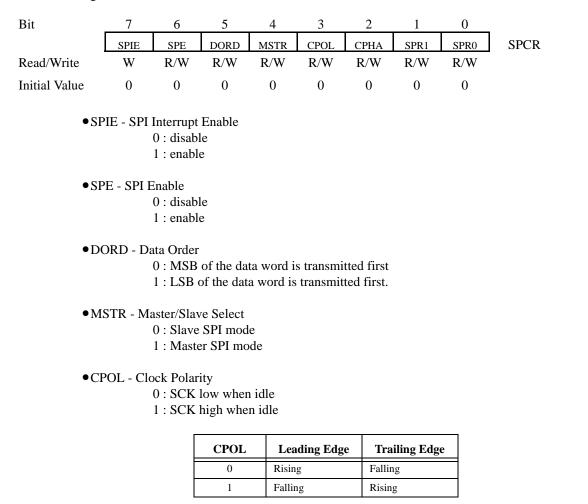

| \$0D(\$2D) | SPCR   | SPIE         | SPE                                     | DORD     | MSTR   | CPOL   | СРНА   | SPR1   | SPR0   |  |  |

| \$0C(\$2C) | UDR    | USART I/O I  | Data Register                           |          |        |        |        |        |        |  |  |

| \$0B(\$2B) | UCSRA  | RXC          | TXC                                     | UDRE     | FE     | DOR    | PE     | U2X    | MPCM   |  |  |

| \$0A(\$2A) | UCSRB  | RXCIE        | TXCIE                                   | UDRIE    | RXEN   | TXEN   | UCSZ2  | RXB8   | TXB8   |  |  |

| \$09(\$29) | UBRRL  | USART Baud   | Rate Register l                         | Low Byte |        |        |        |        |        |  |  |

| \$08(\$28) | ACSR   | ACD          | ACBG                                    | ACO      | ACI    | ACIE   | ACIC   | ACIS1  | ACIS0  |  |  |

| \$07(\$27) | ADMUX  | REFS1        | REFS0                                   | ADLAR    | MUX4   | MUX3   | MUX2   | MUX1   | MUX0   |  |  |

| \$06(\$26) | ADCSRA | ADEN         | ADSC                                    | ADATE    | ADIF   | ADIE   | ADPS2  | ADPS1  | ADPS0  |  |  |

| \$05(\$25) | ADCH   | ADC Data Re  | ADC Data Register High Byte             |          |        |        |        |        |        |  |  |

| \$04(\$24) | ADCL   | ADC Data Re  | ADC Data Register Low Byte              |          |        |        |        |        |        |  |  |

| \$03(\$23) | TWDR   | Two-wire Ser | Two-wire Serial Interface Data Register |          |        |        |        |        |        |  |  |

| \$02(\$22) | TWAR   | TWA6         | TWA5                                    | TWA4     | TWA3   | TWA2   | TWA1   | TWA0   | TWGCE  |  |  |

## 7 Registers

### 7.1 Core

Status Register - SREG

- I Global Interrupt Enable 0 : disable

- 1:enable

- •T Bit Copy Storage

- •C carry flag

- •Z Zero Flag

- •N Negative Flag

- V Two's Complement Overflow Flag

- •S Sign Bit, S = N EXOR V

- •H Half Carry Flag

- •T bit copy storage

Stack Pointer - SPH, SPL

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   |     |

|---------------|------|------|------|------|------|------|-----|-----|-----|

|               | SP15 | SP14 | SP13 | SP12 | SP11 | SP10 | SP9 | SP8 | SPH |

|               | SP7  | SP6  | SP5  | SP4  | SP3  | SP2  | SP1 | SP0 | SPL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |     |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

|               | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   |     |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   |     |

## 7.2 EEPROM

# EEPROM Address Register - EEARH, EEARL

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15          | 14                                  | 13         | 12        | 11        | 10        | 9      | 8           |                                       |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|------------|-----------|-----------|-----------|--------|-------------|---------------------------------------|--|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -           | -                                   | _          | -         | -         | _         | EEAR9  | EEAR8       | EEARH                                 |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EEAR7       | EEAR6                               | EEAR5      | EEAR4     | EEAR3     | EEAR2     | EEAR1  | EEAR0       | EEARL                                 |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7           | 6                                   | 5          | 4         | 3         | 2         | 1      | 0           |                                       |  |  |  |  |  |  |  |  |  |

| Read/Write                                                                                                                                                                                                                                                                                                                                                                                                                                             | R           | R                                   | R          | R         | R         | R         | R/W    | R/W         |                                       |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W         | R/W                                 | R/W        | R/W       | R/W       | R/W       | R/W    | R/W         |                                       |  |  |  |  |  |  |  |  |  |

| Initial Value                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0           | 0                                   | 0          | 0         | 0         | 0         | х      | х           |                                       |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Х           | Х                                   | Х          | Х         | Х         | Х         | Х      | Х           |                                       |  |  |  |  |  |  |  |  |  |

| EEPROM Data R                                                                                                                                                                                                                                                                                                                                                                                                                                          | egister - ] | EEDR                                |            |           |           |           |        |             |                                       |  |  |  |  |  |  |  |  |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7           | 6                                   | 5          | 4         | 3         | 2         | 1      | 0           |                                       |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MSB         |                                     |            |           |           |           |        | LSB         | EEDR                                  |  |  |  |  |  |  |  |  |  |

| Read/Write                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W         | R/W                                 | R/W        | R/W       | R/W       | R/W       | R/W    | R/W         |                                       |  |  |  |  |  |  |  |  |  |

| Initial Value                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0           | 0                                   | 0          | 0         | 0         | 0         | 0      | 0           |                                       |  |  |  |  |  |  |  |  |  |

| EEPROM Contro                                                                                                                                                                                                                                                                                                                                                                                                                                          | l Register  | - EECR                              |            |           |           |           |        |             |                                       |  |  |  |  |  |  |  |  |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7           | 6                                   | 5          | 4         | 3         | 2         | 1      | 0           |                                       |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -           | -                                   | -          | -         | EERIE     | EEMWE     | EEWE   | EERE        | EECR                                  |  |  |  |  |  |  |  |  |  |

| Read/Write                                                                                                                                                                                                                                                                                                                                                                                                                                             | R           | R                                   | R          | R         | R/W       | R/W       | R/W    | R/W         |                                       |  |  |  |  |  |  |  |  |  |

| Initial Value                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0           | 0                                   | 0          | 0         | 0         | 0         | Х      | 0           |                                       |  |  |  |  |  |  |  |  |  |

| ●EF                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | EPROM F<br>0 : disabl<br>1 : enable | e          | errupt Er | able      |           |        |             |                                       |  |  |  |  |  |  |  |  |  |

| ●EF                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EMWE - I    |                                     |            |           |           |           |        |             |                                       |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | When EF<br>write data<br>If EEMW    | a to the E | EPROM     | at the se | lected ad | dress. | k cycles wi | 111                                   |  |  |  |  |  |  |  |  |  |

| - 17                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EWE - EE    |                                     |            | -         |           |           |        |             |                                       |  |  |  |  |  |  |  |  |  |

| <ul> <li>EEWE is the write strobe to the EEPROM.</li> <li>1. Wait until EEWE becomes zero.</li> <li>2. Wait until SPMEN in SPMCR becomes zero.</li> <li>3. Write new EEPROM address to EEAR (optional).</li> <li>4. Write new EEPROM data to EEDR (optional).</li> <li>5. Write a logical one to the EEMWE bit while writing a zero to EEWE in EECR.</li> <li>6. Within four clock cycles after setting EEMWE, write a logical one to EEWE.</li> </ul> |             |                                     |            |           |           |           |        |             |                                       |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                                     | 1          |           |           | . 0.01113 |        |             | Typ. EEPROM Programming Times : 8.5ms |  |  |  |  |  |  |  |  |  |

• EERE - EEPROM Read Enable

EERE – is the read strobe to the EEPROM.

When the correct address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed.

# 7.3 System Clock and Clock Options

Bit 7 6 5 3 2 0 4 1 CAL6 CAL1 OSCCAL CAL7 CAL5 CAL4 CAL3 CAL2 CAL0 Read/Write R/W R/W R/W R/W R/W R/W R/WR/WInitial Value Device Specific Calibration Value

Oscillator Calibration Register - OSCCAL

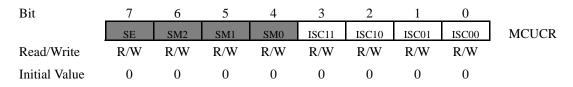

## 7.4 Power Management and Sleep Modes

MCU Control Register - MCUCR

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

|               | SE  | SM2 | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| Initial Value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

•SE - Sleep Enable

0 : disable

1 : enable

• SM2...0 - Sleep Mode Select Bits

| SM2 | SM1 | SM0 | Sleep Mode                                       |

|-----|-----|-----|--------------------------------------------------|

| 0   | 0   | 0   | Idle                                             |

| 0   | 0   | 1   | ADC Noise Reduction                              |

| 0   | 1   | 0   | Power-down                                       |

| 0   | 1   | 1   | Power-save                                       |

| 1   | 0   | 0   | Reserved                                         |

| 1   | 0   | 1   | Reserved                                         |

| 1   | 1   | 0   | Standby (only with external oscillator)          |

| 1   | 1   | 1   | Extended Standby (only with external oscillator) |

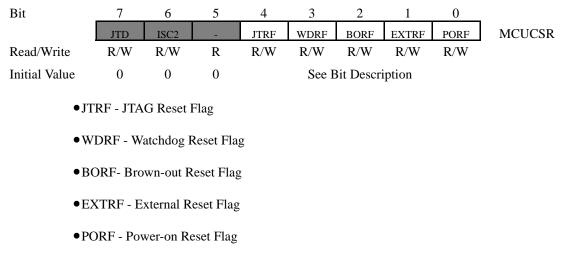

### 7.5 System Control and Reset

### MCU Control and Status Register - MCUCSR

### Watchdog Timer Control Register - WDTCR

| Bit           | 7 | 6 | 5 | 4     | 3   | 2    | 1    | 0    |       |

|---------------|---|---|---|-------|-----|------|------|------|-------|

|               | - | - | - | WDTOE | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write    | R | R | R | R/W   | R/W | R/W  | R/W  | R/W  |       |

| Initial Value | 0 | 0 | 0 | 0     | 0   | 0    | 0    | 0    |       |

• WDTOE - Watchdog Turn-off Enable

This bit must be set when the WDE bit is written to logic zero. Hardware will clear this bit after four clock cycles.

• WDE - Watchdog Enable

- 0 : disable

- 1 : enable

WDE can only be cleared if the WDTOE bit has logic level one.

To disable an enabled Watchdog Timer, the following procedure must be followed:

- In the same operation, write a logic one to WDTOE and WDE. A logic one must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logic 0 to WDE. This disables the Watchdog.

• WP2...WDP0 - Watchdog Timer Prescaler 2...0

| WDP<br>2 | WDP<br>1 | WDP<br>0 | Number of WDT<br>Oscillator Cycles | Typical Time-out for<br>Vcc=3.0V | Typical Time-out for<br>Vcc=5V |

|----------|----------|----------|------------------------------------|----------------------------------|--------------------------------|

| 0        | 0        | 0        | 16384                              | 17.1ms                           | 16.3ms                         |

| 0        | 0        | 1        | 32768                              | 34.3ms                           | 32.5ms                         |

| 0        | 1        | 0        | 65536                              | 68.5ms                           | 65ms                           |

| 0        | 1        | 1        | 131072                             | 0.14s                            | 0.13s                          |

| WDP<br>2 | WDP<br>1 | WDP<br>0 | Number of WDT<br>Oscillator Cycles | Typical Time-out for<br>Vcc=3.0V | Typical Time-out for<br>Vcc=5V |

|----------|----------|----------|------------------------------------|----------------------------------|--------------------------------|

| 1        | 0        | 0        | 262144                             | 0.27s                            | 0.26s                          |

| 1        | 0        | 1        | 524288                             | 0.55s                            | 0.52s                          |

| 1        | 1        | 0        | 1048576                            | 1.1s                             | 1.0s                           |

| 1        | 1        | 1        | 2097152                            | 2.2s                             | 2.1s                           |

### 7.6 Interrupts

General Interrupt Control Register - GICR

| Bit           | 7    | 6    | 5    | 4 | 3 | 2 | 1     | 0    |      |

|---------------|------|------|------|---|---|---|-------|------|------|

|               | INT1 | INT0 | INT2 | - | - | - | IVSEL | IVCE | GICR |

| Read/Write    | R/W  | R/W  | R/W  | R | R | R | R/W   | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0 | 0 | 0 | 0     | 0    |      |

• IVSEL - Interrupt Vector Select

0 : Interrupt vectors are placed at the start of Flash memory

1 : Interrupt vectors are placed at the start of the Boot Loader section

To avoid unintentional changes of Interrupt Vector tables, a special write procedure must be followed to change the IVSEL bit:

- 1. Write the Interrupt Vector Change Enable (IVCE) bit to one.

- 2. Within four cycles, write the desired value to IVSEL while writing a zero to IVCE.

• IVCE - Interrupt Vector Change Enable

The IVCE bit must be written to logic one to enable change of the IVSEL bit. IVCE is cleared by hardware four cycles after it is written or when IVSEL is written. Setting the IVCE bit will disable interrupts.

### 7.7 I/O Ports

Special Function I/O Register - SFIOR

| Bit               | 7           | 6          | 5                 | 4         | 3      | 2      | 1      | 0      |       |

|-------------------|-------------|------------|-------------------|-----------|--------|--------|--------|--------|-------|

|                   | ADTS2       | ADTS1      | ADTS0             | -         | ACME   | PUD    | PSR2   | PSR10  | SFIOR |

| Read/Write        | R/W         | R/W        | R/W               | R         | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0           | 0          | 0                 | 0         | 0      | 0      | 0      | 0      |       |

| • D               |             | un diaahi  | la                |           |        |        |        |        |       |

| •r                | UD - Pull-  | -          | ie<br>ip resistor | rs connec | cted   |        |        |        |       |

|                   |             | 1 : Pull-u | p resistor        | rs discon | nected |        |        |        |       |

| Port A Data Regi  | ister - POF | RTA        |                   |           |        |        |        |        |       |

| Bit               | 7           | 6          | 5                 | 4         | 3      | 2      | 1      | 0      |       |

|                   | PORTA7      | PORTA6     | PORTA5            | PORTA4    | PORTA3 | PORTA2 | PORTA1 | PORTA0 | PORTA |

| Read/Write        | R/W         | R/W        | R/W               | R/W       | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0           | 0          | 0                 | 0         | 0      | 0      | 0      | 0      |       |

| Port A Data Dire  | ction Regi  | ister - DE | ORA               |           |        |        |        |        |       |

| Bit               | 7           | 6          | 5                 | 4         | 3      | 2      | 1      | 0      |       |

|                   | DDA7        | DDA6       | DDA5              | DDA4      | DDA3   | DDA2   | DDA1   | DDA0   | DDRA  |

| Read/Write        | R/W         | R/W        | R/W               | R/W       | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0           | 0          | 0                 | 0         | 0      | 0      | 0      | 0      |       |

| Port A Input Pins | s Address   | - PINA     |                   |           |        |        |        |        |       |

| Bit               | 7           | 6          | 5                 | 4         | 3      | 2      | 1      | 0      |       |

|                   | PINA7       | PINA6      | PINA5             | PINA4     | PINA3  | PINA2  | PINA1  | PINA0  | PINA  |

| Read/Write        | R/W         | R/W        | R/W               | R/W       | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0           | 0          | 0                 | 0         | 0      | 0      | 0      | 0      |       |

| Port B Data Regi  | ster - POF  | ХТВ        |                   |           |        |        |        |        |       |

| Bit               | 7           | 6          | 5                 | 4         | 3      | 2      | 1      | 0      |       |

|                   | PORTB7      | PORTB6     | PORTB5            | PORTB4    | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write        | R/W         | R/W        | R/W               | R/W       | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0           | 0          | 0                 | 0         | 0      | 0      | 0      | 0      |       |

| Port B Data Dire  | ction Regi  | ster - DE  | ORB               |           |        |        |        |        |       |

| Bit               | 7           | 6          | 5                 | 4         | 3      | 2      | 1      | 0      |       |

|                   | DDB7        | DDB6       | DDB5              | DDB4      | DDB3   | DDB2   | DDB1   | DDB0   | DDRB  |

| Read/Write        | R/W         | R/W        | R/W               | R/W       | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0           | 0          | 0                 | 0         | 0      | 0      | 0      | 0      |       |

# Port B Input Pins Address - PINB

| Bit               | 7          | 6         | 5      | 4      | 3      | 2      | 1      | 0      |       |

|-------------------|------------|-----------|--------|--------|--------|--------|--------|--------|-------|

|                   | PINB7      | PINB6     | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | PINB  |

| Read/Write        | R/W        | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0          | 0         | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port C Data Regi  | ster - POR | RTC       |        |        |        |        |        |        |       |

| Bit               | 7          | 6         | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                   | PORTC7     | PORTC6    | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

| Read/Write        | R/W        | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0          | 0         | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port C Data Direc | ction Regi | ster - DD | RC     |        |        |        |        |        |       |

| Bit               | 7          | 6         | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                   | DDC7       | DDC6      | DDC5   | DDC4   | DDC3   | DDC2   | DDC1   | DDC0   | DDRC  |

| Read/Write        | R/W        | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0          | 0         | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port C Input Pins | Address -  | - PINC    |        |        |        |        |        |        |       |

| Bit               | 7          | 6         | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                   | PINC7      | PINC6     | PINC5  | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  | PINC  |

| Read/Write        | R/W        | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0          | 0         | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port D Data Regi  | ster - POF | RTD       |        |        |        |        |        |        |       |

| Bit               | 7          | 6         | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                   | PORTD7     | PORTD6    | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

| Read/Write        | R/W        | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0          | 0         | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port D Data Dire  | ction Regi | ster - DE | ORD    |        |        |        |        |        |       |

| Bit               | 7          | 6         | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                   | DDD7       | DDD6      | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | DDRD  |

| Read/Write        | R/W        | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial Value     | 0          | 0         | 0      | 0      | 0      | 0      | 0      | 0      |       |

# Port D Input Pins Address - PIND

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | PIND7 | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 | PIND |

| Read/Write    | R/W   |      |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |      |

| DDxn | PORTxn | PUD (in SFIOR) | I/O    | Pull-up | Comment                                     |

|------|--------|----------------|--------|---------|---------------------------------------------|

| 0    | 0      | Х              | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | 0              | Input  | Yes     | Pxn will source current if ext. pulled low. |

| 0    | 1      | 1              | Input  | No      | Tri-state (Hi-Z)                            |

| 1    | 0      | Х              | Output | No      | Output Low (Sink)                           |

| 1    | 1      | Х              | Output | No      | Output High (Source)                        |

### 7.8 External Interrupts

MCU Control Register - MCUCR

• ISC11, ISC10 - Interrupt Sense Control 1

| ISC11 | ISC10 | Description                                        |

|-------|-------|----------------------------------------------------|

| 0     | 0     | Low level of INT1 generates interrupt request      |

| 0     | 1     | Logical change on INT1 generates interrupt request |

| 1     | 0     | Falling edge of INT1 generates interrupt request   |

| 1     | 1     | Rising edge of INT1 generates interrupt request    |

### • ISC01, ISC00 - Interrupt Sense Control 0

| ISC01 | ISC00 | Description                                        |

|-------|-------|----------------------------------------------------|

| 0     | 0     | Low level of INT0 generates interrupt request      |

| 0     | 1     | Logical change on INTO generates interrupt request |

| 1     | 0     | Falling edge of INT0 generates interrupt request   |

| 1     | 1     | Rising edge of INT0 generates interrupt request    |

### MCU Control and Status Register - MCUCSR

| Bit           | 7   | 6    | 5 | 4    | 3    | 2    | 1     | 0    |        |

|---------------|-----|------|---|------|------|------|-------|------|--------|

|               | JTD | ISC2 | _ | JTRF | WDRF | BORF | EXTRF | PORF | MCUCSR |

| Read/Write    | R/W | R/W  | R | R/W  | R/W  | R/W  | R/W   | R/W  |        |

| Initial Value | 0   | 0    | 0 |      |      |      |       |      |        |

• ISC2 - Interrupt Sense Control 2 0 : Falling edge on INT2 generates interrupt request

1 : Rising edge on INT2 generates interrupt request

General Interrupt Control Register - GICR

| Bit           | 7    | 6    | 5    | 4 | 3 | 2 | 1     | 0    |      |

|---------------|------|------|------|---|---|---|-------|------|------|

|               | INT1 | INT0 | INT2 | - | - | - | IVSEL | IVCE | GICR |

| Read/Write    | R/W  | R/W  | R/W  | R | R | R | R/W   | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0 | 0 | 0 | 0     | 0    |      |

• INT1 - External Interrupt Request 1 Enable

0 : disable

# • INTO - External Interrupt Request 0 Enable 0 : disable 1 : enable

• INT2 - External Interrupt Request 2 Enable 0 : disable 1 : enable

General Interrupt Flag Register - GIFR

| Bit           | 7     | 6     | 5     | 4 | 3 | 2 | 1 | 0 |      |

|---------------|-------|-------|-------|---|---|---|---|---|------|

|               | INTF1 | INTF0 | INTF2 | - | - | - | - | - | GIFR |

| Read/Write    | R/W   | R/W   | R/W   | R | R | R | R | R |      |

| Initial Value | 0     | 0     | 0     | 0 | 0 | 0 | 0 | 0 |      |

• INTF1 - External Interrupt Flag 1

1 : Interrupt Request

Flag is cleared when the interrupt routine is executed. The flag can be cleared by writing a logical one to it.

• INTF0 - External Interrupt Flag 0

1 : Interrupt Request

Flag is cleared when the interrupt routine is executed. The flag can be cleared by writing a logical one to it.

• INTF2 - External Interrupt Flag 2

1 : Interrupt Request

Flag is cleared when the interrupt routine is executed. The flag can be cleared by writing a logical one to it.

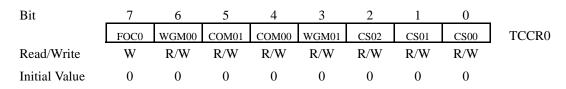

### 7.9 8-bit Timer/Counter0 with PWM

Timer/Counter Control Register - TCCR0

• FOC0 - Force Output Compare

- Only active when the WGM00 bit specifies a non-PWM mode. When writing a logical one to the FOC0 bit, an immediate compare match is forced on the Waveform Generation unit. The OC0 output is changed according to its COM01:0 bits setting. Note that the FOC0 bit is implemented as a strobe. Therefore it is the value present in the COM01:0 bits that determines the effect of the forced compare. A FOC0 strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0 as TOP.

- The FOC0 bit is always read as zero.

•WGM01:0 - Waveform Generation Mode

These bits control the counting sequence of the counter, the source for the maximum (TOP) counter value, and what type of Waveform Generation to be used.

| Mode | WGM01 | WGM00 | Timer/Counter Mode of<br>Operation | ТОР  | Update of<br>OCR0 | TOV0 Flag Set-on |  |

|------|-------|-------|------------------------------------|------|-------------------|------------------|--|

| 0    | 0     | 0     | Normal                             | 0xFF | Immediate         | MAX              |  |

| 1    | 0     | 1     | PWM, Phase Correct                 | 0xFF | TOP               | BOTTOM           |  |

| 2    | 1     | 0     | CTC                                | )CR0 | Immediate         | MAX              |  |

| 3    | 1     | 1     | Fast PWM                           | 0xFF | ТОР               | MAX              |  |

| Compare Output Mode, non-PWM mode |       |                                         |  |  |  |  |  |  |

|-----------------------------------|-------|-----------------------------------------|--|--|--|--|--|--|

| COM01                             | COM00 | Description                             |  |  |  |  |  |  |

| 0                                 | 0     | Normal port operation, OC0 disconnected |  |  |  |  |  |  |

| 0                                 | 1     | Toggle OC0 on compare match             |  |  |  |  |  |  |

| 1                                 | 0     | Clear OC0 on compare match              |  |  |  |  |  |  |

| 1                                 | 1     | Set OC0 on compare match                |  |  |  |  |  |  |

|       | Compare Output Mode, fast-PWM mode |                                            |  |  |  |  |  |  |  |

|-------|------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|

| COM01 | COM00                              | Description                                |  |  |  |  |  |  |  |

| 0     | 0                                  | Normal port operation, OC0 disconnected    |  |  |  |  |  |  |  |

| 0     | 1                                  | Reserved                                   |  |  |  |  |  |  |  |